In the world of electronics, we have an insatiable need for speed. Whether it is streaming 4K video, training AI models in a data center, or transferring files over USB-C, data needs to move fast.

But there is a physical limit to how fast we can push data through a wire. This is where SerDes comes in.

If you have ever looked at the specs of a PCIe slot, an Ethernet port, or an FPGA and wondered how they achieve Gigabits of throughput, the answer is SerDes.

This guide will break down what SerDes is, why we abandoned the old "parallel" ways, and the magic technology that makes modern high-speed communication possible.

1. The Definition: What does SerDes stand for?

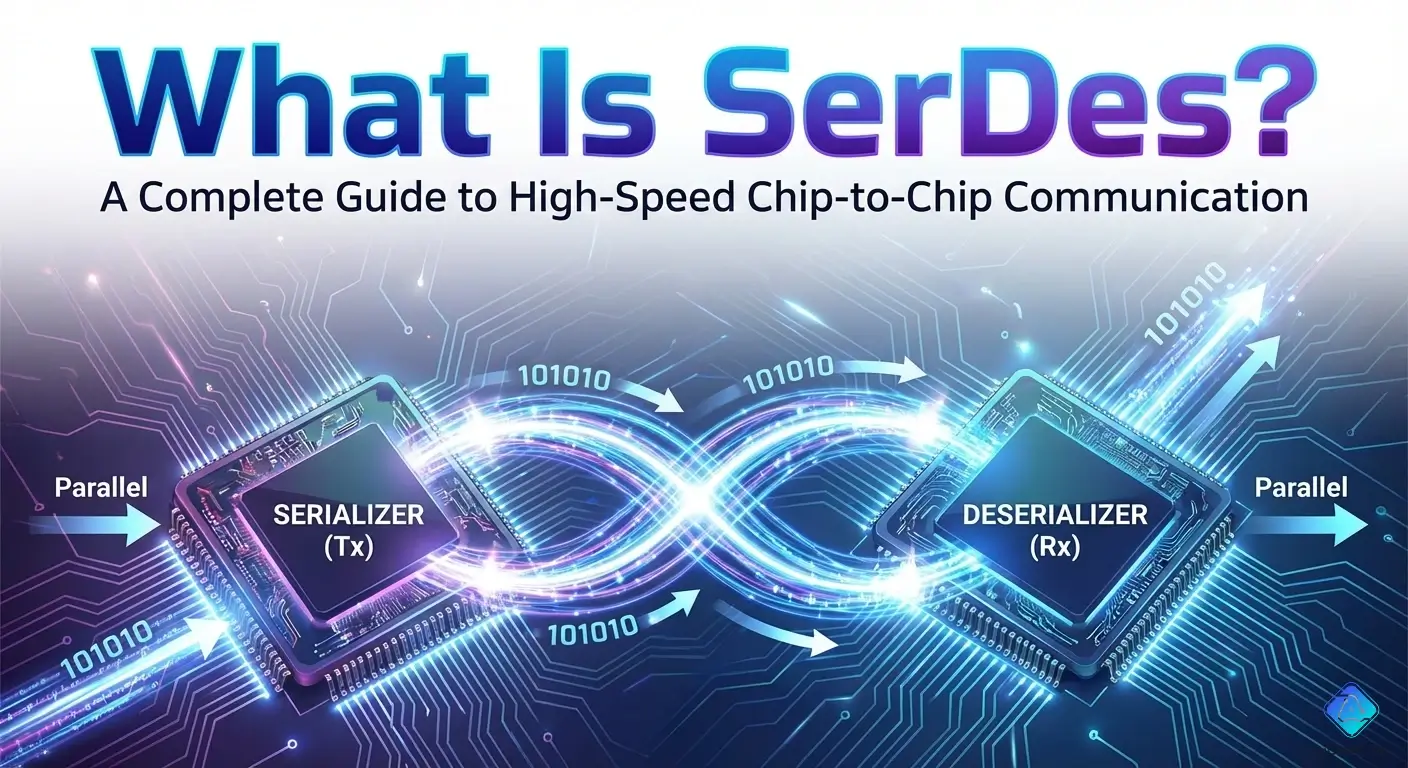

SerDes is an acronym for SERializer / DESerializer.

It is a pair of functional blocks commonly found in high-speed chips (like FPGAs, ASICs, and processors) used to convert data between two formats:

- Parallel Data: Used inside the chip (slow, wide, easy to process).

- Serial Data: Used between chips (fast, narrow, efficient for travel).

The "Highway vs. Tunnel" Analogy

Think of data like cars.

- Parallel (Inside the Chip): Imagine an 8-lane highway where cars drive side-by-side at 50 mph. It moves a lot of traffic, but it takes up a huge amount of space (width).

- Serial (SerDes): The highway narrows down to a single-lane tunnel, but the cars zoom through at 5,000 mph.

SerDes is the toll booth at the entrance and exit of that tunnel, organizing the cars into a single line to shoot them across at hypersonic speeds.

2. The Problem with Parallel Buses (Why we need SerDes)

In the 90s, we used parallel buses (like the old ribbon cables in PCs). To make them faster, we added more wires. 8 wires, 16 wires, 32 wires...

But eventually, physics got in the way.

The "Clock Skew" Problem

In a parallel bus, you send a clock signal along with the data wires. The receiver waits for the "tick" of the clock to read all the data wires at once. At high speeds (Gigahertz), electricity travels at different speeds through slightly different wire lengths. One bit might arrive 1 nanosecond later than the others. This is Clock Skew. If the bits don't arrive together, the data is corrupted.

The "Pin Count" Problem

Chips have a limited number of pins. If you need to transmit 100 Gigabits of data using a parallel bus, you might need thousands of pins. That makes the chip physically huge and expensive. SerDes allows you to send that same data over just 2 or 4 pins.

3. How SerDes Works: The Architecture

A basic SerDes link consists of three main parts: The Transmitter, The Channel, and The Receiver.

Step 1: The Serializer (PISO)

Inside the transmitting chip, data is processed in parallel (e.g., 8 bits at a time). The Serializer takes these 8 bits and lines them up one by one. This is called PISO (Parallel-In, Serial-Out).

Step 2: The Channel (Differential Signaling)

The data is shot out over a pair of wires called a Differential Pair ($D+$ and $D-$).

- Instead of measuring voltage against the ground (Single-Ended), SerDes measures the difference between two wires.

- Why? Noise Immunity. If external electrical noise hits the wire, it hits both wires equally. The difference between them remains the same, preserving the data.

Step 3: The Deserializer (SIPO)

The receiving chip takes the high-speed serial stream and slows it down, stacking the bits back into 8-bit groups for the chip to process. This is SIPO (Serial-In, Parallel-Out).

The Magic: Clock Data Recovery (CDR)

This is the most critical concept in SerDes. In a parallel bus, you have a separate wire for the "Clock" (the metronome). In SerDes, there is no clock wire. The clock information is embedded inside the data itself by ensuring the data transitions (flips from 0 to 1) frequently enough.

The Receiver uses a block called CDR (Clock Data Recovery) to "guess" the speed of the incoming data and lock onto its rhythm.

4. Signal Integrity: Keeping the Data Clean

Sending data at 10Gbps or 56Gbps over copper traces is messy. The signal degrades, fades, and bounces. To fix this, SerDes uses Equalization.

- Pre-Emphasis (Tx): The transmitter shouts louder at the beginning of a bit to ensure it survives the journey.

- CTLE / DFE (Rx): The receiver uses complex math (Continuous Time Linear Equalization / Decision Feedback Equalization) to filter out echoes and noise, reconstructing the original "clean" square wave.

5. Where is SerDes Used?

You are using SerDes right now. It is the physical layer (PHY) for almost all modern high-speed standards:

- PCI Express (PCIe): Connecting GPUs and NVMe SSDs to the CPU.

- Ethernet (SFP+ / QSFP): The backbone of the internet.

- USB (3.0 and newer): High-speed data transfer.

- SATA / SAS: Hard drive connections.

- HDMI / DisplayPort: Sending video signals to your monitor.

6. Conclusion

SerDes is the unsung hero of the digital age. By solving the limitations of parallel buses—specifically clock skew and pin density—it allowed us to scale from Megabits to Terabits.

As we move toward AI and Hyperscale computing, SerDes continues to evolve (moving from NRZ to PAM4 modulation), but the core concept remains the same: serialize it, send it fast, and recover it on the other side.

Looking for High-Speed SerDes Chips? Whether you are designing a custom FPGA board or repairing networking gear, finding the right ICs is critical. Visit Aichiplink.com to search for SerDes transceivers, FPGAs, and Retimers.

Written by Jack Elliott from AIChipLink.

AIChipLink, one of the fastest-growing global independent electronic components distributors in the world, offers millions of products from thousands of manufacturers, and many of our in-stock parts is available to ship same day.

We mainly source and distribute integrated circuit (IC) products of brands such as Broadcom, Microchip, Texas Instruments, Infineon, NXP, Analog Devices, Qualcomm, Intel, etc., which are widely used in communication & network, telecom, industrial control, new energy and automotive electronics.

Empowered by AI, Linked to the Future. Get started on AIChipLink.com and submit your RFQ online today!

Frequently Asked Questions

What does SerDes stand for?

SerDes stands for Serializer / Deserializer.

Why is SerDes used instead of parallel buses?

It avoids clock skew, reduces pin count, and supports much higher speeds.

Does SerDes require a separate clock signal?

No. The clock is recovered from the data using CDR (Clock Data Recovery).

Where is SerDes commonly used?

In PCIe, Ethernet, USB, SATA, HDMI, and DisplayPort interfaces.

What limits SerDes performance at high speeds?

Signal integrity issues such as noise, loss, and crosstalk.

.png&w=256&q=75)