Table of Contents

- 1.0 What is the EPF10K30BC356-4?

- 1.1 An Overview of the Altera FLEX 10K Family

- 1.2 Decoding the Part Number: EPF10K30BC356-4

- 1.3 Key Features from the Datasheet

- 2.0 EPF10K30BC356-4 Key Technical Specifications

- 2.1 Logic, Gates, and Memory Specs

- 2.2 Operating Voltage and Power

- 2.3 EPF10K30BC356-4 Pinout and BGA-356 Package Details

- 3.0 EPF10K30BC356-4 Applications and Obsolescence

- 3.1 Common Legacy Applications

- 3.2 EPF10K30BC356-4 vs. Modern FPGAs

- 3.3 Finding an EPF10K30BC356-4 Replacement

- 4.0 Programming and Configuring the EPF10K30BC356-4

- 4.1 Required Software: Altera Quartus II

- 4.2 Configuration Devices and Methods

- 5.0 Frequently Asked Questions (FAQ)

Have you ever come across a long-lifecycle piece of industrial equipment, telecom hardware, or medical device and wondered what makes it tick? Chances are, you'll find a workhorse chip like the IC EPF10K30BC356-4 at its heart. While not a modern component, this legacy CPLD (Complex Programmable Logic Device) from Altera (now Intel) is a critical piece of technology responsible for the "glue" logic in thousands of systems still in operation today. In fact, the market for maintaining legacy systems, valued in the billions, relies heavily on the availability of these specific components. For engineers, designers, and supply chain managers, understanding this device isn't just a history lesson—it's essential for maintenance, repair, and long-term product support. This guide will serve as your technical deep-dive into the EPF10K30BC356-4, covering its specifications, applications, and how to work with it today.

1.0 What is the EPF10K30BC356-4?

The IC EPF10K30BC356-4 is a high-density Complex Programmable Logic Device (CPLD) that was part of the groundbreaking Altera FLEX 10K family. Unlike simpler CPLDs, the FLEX 10K series was one of the first to embed significant blocks of RAM, making it a "first-generation" FPGA in many respects. It's an SRAM-based device, meaning it needs to be configured by an external source at power-up.

1.1 An Overview of the Altera FLEX 10K Family

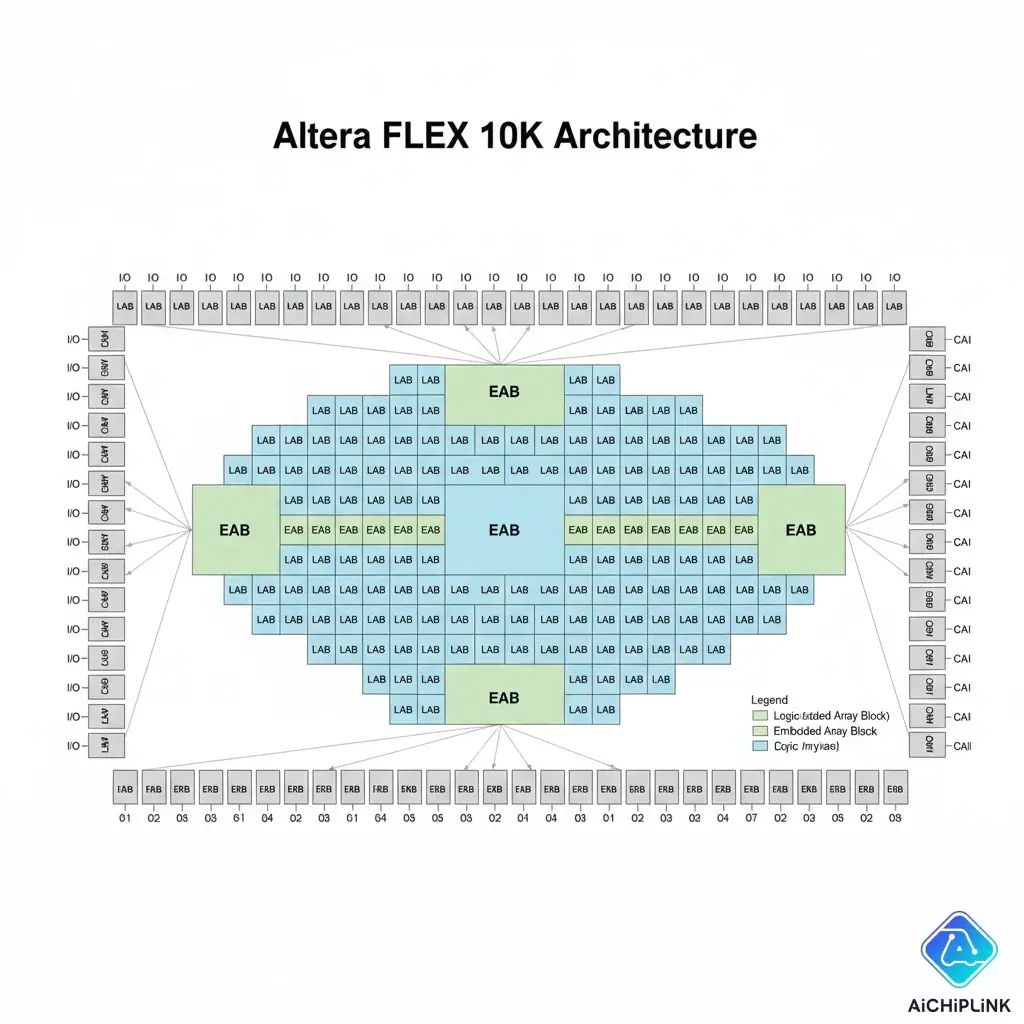

The FLEX 10K family was a game-changer when it was released, as it provided a flexible and cost-effective alternative to ASICs (Application-Specific Integrated Circuits). Its architecture is based on two main structures: * **Logic Array Blocks (LABs):** These are the primary building blocks for your logic. Each LAB contains 8 Logic Elements (LEs), which are based on 4-input look-up tables (LUTs), a flip-flop, and carry-chain logic. * **Embedded Array Blocks (EABs):** This was the key innovation. EABs are flexible 2,048-bit blocks of RAM that can be configured as RAM, ROM, or FIFOs. The EPF10K30BC356-4 has 6 of these EABs, for a total of 12,288 bits of on-chip RAM.1.2 Decoding the Part Number: EPF10K30BC356-4

Understanding the part number is the first step to understanding the chip's capabilities: * **EPF10K30:** The device family (FLEX 10K) and typical logic gates (30,000). * **B:** A specific revision or feature set of the chip. * **C356:** The package type, which is a 356-pin Ball Grid Array (BGA). * **-4:** This is the **speed grade**. A -4 is a standard commercial speed grade, with faster (and more expensive) -1, -2, and -3 versions also existing.1.3 Key Features from the Datasheet

This CPLD was popular for a reason. It packed a ton of features for its time: * **30,000 typical gates** * **1,728 Logic Elements (LEs)** * **12,288 bits of on-chip RAM** (via 6 EABs) * In-System Programmability (ISP) via JTAG * **MultiVolt™ I/O:** Allows the 5V device to interface directly with 3.3V logic levels.

2.0 EPF10K30BC356-4 Key Technical Specifications

For an engineer, the datasheet is the source of truth. Here are the hard numbers you need to know for the IC EPF10K30BC356-4.

2.1 Logic, Gates, and Memory Specs

This table provides a clear comparison of the device's core resources.| Specification | Value |

|---|---|

| Device Family | FLEX 10K |

| Logic Elements (LEs) | 1,728 |

| Logic Array Blocks (LABs) | 216 |

| Typical Gates | 30,000 |

| Max Gates | 69,000 |

| Embedded Array Blocks (EABs) | 6 |

| Total RAM Bits | 12,288 |

| Max User I/O | 246 |

2.2 Operating Voltage and Power

This is a 5V device, which is a critical piece of information for modern designers used to 3.3V or 1.8V. * **Core Supply Voltage (VCCINT):** 5.0V * **I/O Supply Voltage (VCCIO):** 3.3V or 5.0V, supporting the MultiVolt™ interface.2.3 EPF10K30BC356-4 Pinout and BGA-356 Package Details

The **BGA-356** package is a 356-pin Ball Grid Array. This is a surface-mount package that requires specialized assembly equipment (i.e., not hand-solderable). The 356 pins provide access to the 246 user I/O pins, as well as all necessary power, ground, and configuration pins.Expert Tip: When dealing with BGA packages, especially on older designs, getting a correct pinout diagram is non-negotiable. Always refer to the official Altera datasheet or a trusted source, as a single incorrect connection can be impossible to fix after assembly.

3.0 EPF10K30BC356-4 Applications and Obsolescence

Understanding this CPLD today is a tale of two parts: what it was used for, and how you can replace it.

3.1 Common Legacy Applications

The **IC EPF10K30BC356-4** was a workhorse in the late 1990s and 2000s. You will most commonly find it in: * **Telecommunications:** As logic for line cards, switches, and early network processing. * **Industrial Control:** In PLCs, motor control systems, and custom automation equipment. * **Test and Measurement:** As the core logic for signal generators, logic analyzers, and data acquisition cards. * **Aerospace & Defense:** In long-lifecycle products that value reliability and a proven track record.3.2 EPF10K30BC356-4 vs. Modern FPGAs

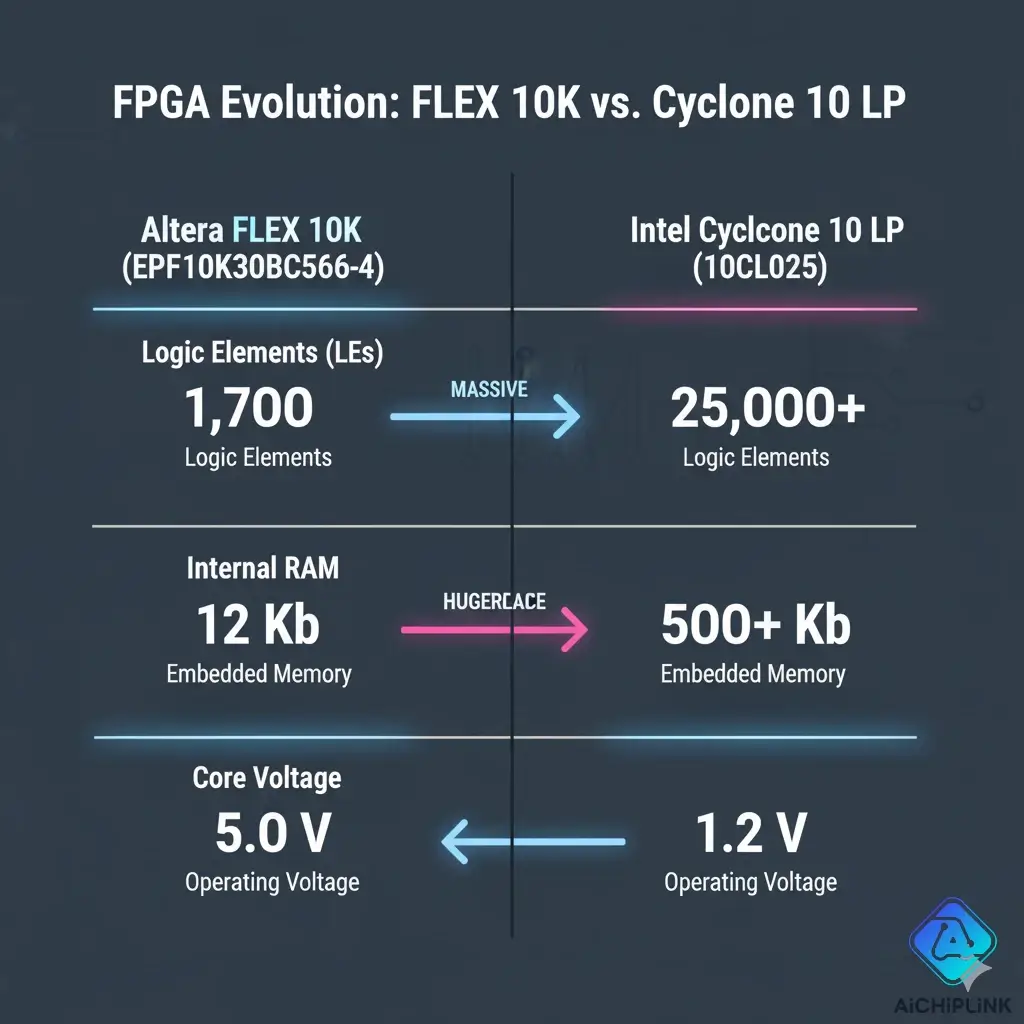

While this device was powerful, technology has marched on. A **2023**-era entry-level FPGA from the Intel Cyclone or AMD Spartan series would outperform it by orders of magnitude for a fraction of the cost.

3.3 Finding an EPF10K30BC356-4 Replacement

This device is **obsolete and not recommended for new designs**. If you are looking for a replacement, you have two options: 1. **Pin-for-Pin Replacement:** You must find an identical **EPF10K30BC356-4 from a reliable distributor** of obsolete components. This is the only option for simple repair and maintenance, as the BGA package is not compatible with other devices. 2. **Functional Redesign:** This involves a complete re-engineering of the PCB to use a modern FPGA. This is a very expensive and complex process, making it a last resort.4.0 Programming and Configuring the EPF10K30BC356-4

If you have a board with one of these CPLDs, you can't just plug it into a modern PC and expect it to work. You are dealing with legacy tools.

4.1 Required Software: Altera Quartus II

Modern Intel Quartus Prime **does not support** the FLEX 10K family. To program or recompile logic for this chip, you must find and install a legacy version of the **Altera Quartus II** software (typically version 9.1 or earlier). This software is the only tool that contains the necessary device files and compilation algorithms.4.2 Configuration Devices and Methods

Being SRAM-based, the EPF10K30BC356-4 must be configured at every power-on. This is usually accomplished in one of two ways: * **Configuration PROM:** The CPLD is connected to a dedicated Altera EPC-series configuration PROM, which automatically loads the data into the CPLD on startup. * **Host CPU:** A microcontroller or processor on the board writes the configuration data directly to the CPLD through a JTAG or passive serial interface.In Conclusion

The IC EPF10K30BC356-4 represents a significant milestone in the history of programmable logic. While it has been surpassed in every metric by modern FPGAs, it remains a critical component for the service and maintenance of countless industrial, medical, and telecom systems still in operation. Understanding its legacy architecture, 5V operation, and specific software requirements is the key to successfully supporting these long-lifecycle products. As these systems continue to age, the demand for reliable sources of obsolete components will only grow.

If you are in the difficult position of sourcing this or other obsolete CPLDs, you need a partner who specializes in hard-to-find components. Contact AichipLink today to check our inventory and secure the legacy parts you need to keep your systems running.

Frequently Asked Questions

What software do I use to program the EPF10K30BC356-4?

You must use a legacy version of the **Altera Quartus II software** (e.g., v9.1 or older). Modern Intel Quartus Prime software does not support the FLEX 10K device family. You will also need a compatible programming cable, like an Altera USB-Blaster.

What is the EPF10K30BC356-4?

The **EPF10K30BC356-4** is a legacy 5V Complex Programmable Logic Device (CPLD) from the Altera FLEX 10K family. It features 30,000 typical gates, 1,728 logic elements, and 12,288 bits of on-chip RAM. It is housed in a 356-pin BGA package and has a -4 speed grade.

Is the EPF10K30BC356-4 still in production?

No. The entire Altera FLEX 10K family, including this device, is considered obsolete and has been discontinued. It is not recommended for new designs (NRND). Its primary market today is for repair and maintenance of existing systems.

What is the difference between a CPLD and an FPGA?

This is a common question! Generally, a CPLD has a non-volatile, sum-of-products architecture, making it good for simple "glue" logic. An FPGA is SRAM-based, much denser, and has a flexible lookup-table (LUT) architecture for complex digital signal processing. The **<u><a href="https://en.wikipedia.org/wiki/Complex_programmable_logic_device" target="_blank">FLEX 10K family</a></u>** was one of the first to blur this line, which is why Altera marketed it as a CPLD with FPGA-like features.

What is the operating voltage for the EPF10K30BC356-4?

The core voltage (VCCINT) is **5.0V**. It also features a MultiVolt™ I/O, allowing its I/O banks to be powered at 3.3V to interface with lower-voltage logic.

.png&w=256&q=75)